Menu

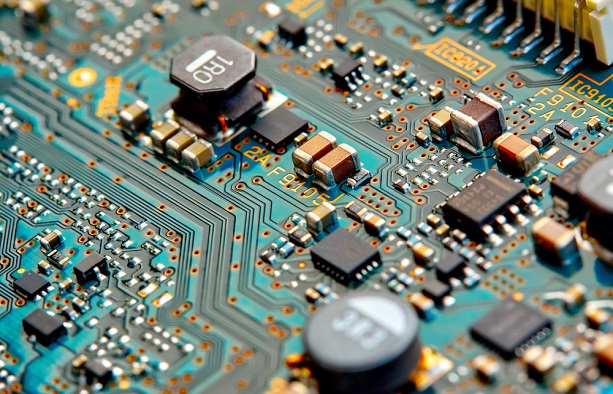

ASIC Design

At a CAGR of % from 2022 to 2028, the size of the global market for ASIC design services is expected to increase from USD million in 2021 to USD million in 2028.

It is difficult to develop high-quality RTL since the chip must have sufficient performance while consuming little space and power. To get around this, we make use of our team’s decades of knowledge and adhere to a strict design checklist. With a solution that tackles the particular issue you’re attempting to solve, we can assist competence in front-end RTL design and SoC integration of SoCs and IPs with millions of gates across a range of industry verticals, including networking, multimedia, mobile, and CPUs.

Design

- SoC Architecture and IP Micro Arch

- SoC and Sub-System Integration

- DFT RTL Design and Integration

- RTL Quality Checks

- Synthesis, Timing, Caliber and FEV Timing, Constraints and Constraints Validation

FPGA

- ASIC and IP Prototyping with FPGA

- FPGA and System Architecture Design

- RTL Design from Micro-architecture

- RTL Verification: UVM/OVM and other Methodology

- Porting to Different FPGA, FPGA to ASIC Porting and Vice Versa

- Board Design and Bring up

- FPGA Fitment, Bitmap Generation

- FPGA/System Validation on Board

Expertise

- IPs: USB/ SATA/ DDR/ LPPP/ AHB/AXI/ SD/ MMC/ HDMI

- IP Block Development: Reusable, Pipelined, CDC, Lint, DFT, HW-SW partitioning

- Technologies:X86 Processor, ARM/DSP Based SoC, 4G/LTE, Switching, BTLE/NFC

Languages: VHDL, Verilog and System Verilog, C/ C++ - Methodologies: OVM/ UVM/ VVM

- SoCs: Mobile Processor, Graphics Processor, Network Processor, Automotive, LTE Modem chip

- Misc: IFV, PSL, Lower power verification in UPF

- Integration: Block integration, Clocks and Reset, Clock gating, DFT and DFD, Lint, CDC

- Protocols: AMBA CHI/AXI/AHB/APB, MIPI (DSI, CSI, Slimbus, Soundwire, Unipro, NAND Flash); PCIe; SAS/SATA; SDIO Host/Device/Memory/Combo; I2C, SPI, UART, MDIO