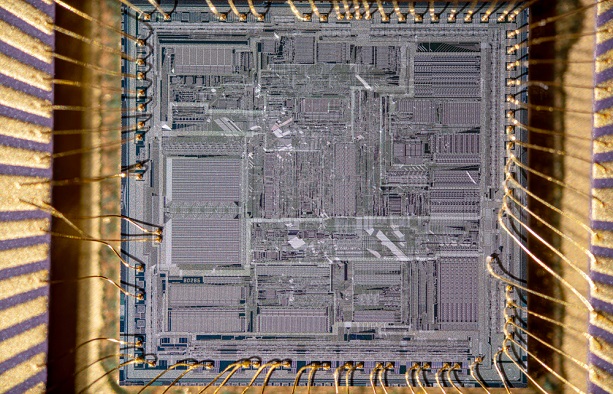

Analog Design & Layout

In order to ensure client success in this cutthroat market, we must select the best design while introducing a new product. The product development team receives assistance from our design team throughout the entire VLSI engineering process.

Based on various specifications, we assist businesses with their analogue circuit design and layout needs in order to create circuit blocks or subsystems that are integrated into bigger, customer-designed chips.

Our design team is capable of making the essential trade-offs to optimise the design performance, area, power, time to market, product reliability, and cost of your design or product. We have the relevant skills to produce creative analogue solutions.

We do have solid experience with memory solutions, IO solutions, standard cell solutions, etc.

Capabilities

- Analog and mixed signal building blocks

- High precision mixed-signal circuits

- Layout with HV devices

- Full chip integration (Analog-on-top or digital-on-top)

- Integration of high power with high accuracy circuits

- Experience with CMOS, BCD and SOI

- Complete Analog Design life-cycle from specs to post-silicon validation

- Successful delivery of multiple std cell libraries from 10nm to 90 nm, including High performance, High density, 11T, 9T, 7.5T, 6T design.

Expertise

- Worked on Ips: SerDes (10, 16, 30 & 56 Gbps), DDRphy, USB 2.0, MIPIphy, and Power management

- Handled expanded portfolios of Data converters, clock circuits such as PLL, DLL & oscillators, Regulators, Bias, Bandgap references, Temperature sensors, UVLOs, etc.

- Expertise on CMOS/FinFET process node: 3nm, 5nm, 7nm, 10nm, 14nm, 22nm, 45nm, 65nm, 90nm, 130nm, 180nm ,350nm to 500nm

- Multiple full chips and IP level tape out have been done successfully with first-pass silicon

- Worked on Memory with a variety of architecture: multi-port memories, SRAM, Memory compilers, Register files & custom memories on cutting-edge technologies

Worked on IO layouts from 250nm to 3nm technologies including GPIOs, LVCMOS, LVTTL, LVDS, DDR, etc. with an Analog/Power ring - ESD requirements for HBM, MM, and CDM

- Std cell library development.

- Process migration for older libraries

- Std cell Characterization

- Multi-port Memory design & layout.

- Memory compilers and Register files.

- Memory Characterization.